Continuing the discussion from Purism on creating an SBC:

Unfortunately, NXP won’t be creating a “fully open SoC” if it is sticks RISC-V cores on a i.MX SoC, since there is still the proprietary GPU, VPU, I/O, etc., but it will get us one step closer by using a free/open Instruction Set Architecture. I doubt that NXP will release the source code for its CPU cores. The license for work done by the OpenHW Group is Apache 2.0, which means that NXP has no obligation to release the code for the CPU core that it uses.

On the other hand, we should give NXP credit if it contributes to the OpenHW’s Ariane 64-bit CPU core or helps support its development in some way. So far, however, I don’t see any NXP contributions to Ariane when I do a search in the commits. (It is possible that NXP employees are doing commits, but not identifying themselves as NXP employees.) If the OpenHW cores keep getting better, there is the possibility that some company will use them to produce a free/open hardware CPU in the future, and people can start creating free/open FPGA’s on their own using the OpenHW cores.

I’m hopeful about a future i.MX+RISC-V SoC actually becoming a reality, because NXP has a financial incentive to dump ARM Holding’s straight-jacket and its licensing fees. Not having to worry about ARM Holding’s restrictions will give NXP a great deal of freedom to design for the automotive and IoT markets. NXP has the chance to establish itself as the premier RISC-V SoC maker.

Among the companies currently working on RISC-V, NXP is the most likely to bring it to market in a serious way. Alibaba only wants to make specialized internet servers for its own use. Qualcomm and Western Digital are interested in using RISC-V cores, but they are outsourcing the development by investing in SiFive, rather than doing the dev work themselves, which means that they aren’t betting their companies’ future on it. At any rate, Western Digital only wants RISC-V for its own use in its SSDs. If Qualcomm were really serious, it would do the work in house like NXP is doing, but Qualcomm has too much of a lock on its current market to play the role of a disruptor. SiFive has big plans but it doesn’t have the resources, experience and long customer relationships to bring RISC-V to market in a major way, which is why I think NXP is best positioned to become the RISC-V leader.

NXP is probably the best company that we can hope for to undertake this. It has the resources ($9.4 billion in revenue in 2018) and the engineering depth from Freescale in Austin, TX to make RISC-V CPUs a reality. Intel and AMD are better than NXP in terms of contributing to the mainline Linux kernel, but they both have an entrenched niche to protect with the x86 architecture.

Among the mobile processor makers, only NXP, Rockchip and Broadcom care about FOSS (maybe you could add nVidia, but it no longer wants to make mobile Tegra processors). NXP has far more resources to throw at the problem than Rockchip and Broadcom processors are still not bootable with a 100% FOSS stack. NXP also thinks longer term, since it designs for 10 or 15 year manufacturing cycles, rather than 5 year cycles, so investing in RISC-V makes more sense on those time scales. Its market niches in automotive electronics, secure identification and digital networking also don’t demand leading-edge performance, so it can risk developing a platform that may not have as good of performance as ARM, but is able to beat ARM in terms of flexibility, customization and no licensing fees/restrictions.

Of course, it will be a lot of work to migrate all the software to a new ISA, but with FOSS, it is doable, whereas it would be very difficult to migrate the Google Play Store or Apple Store from ARM to RISC-V, because it is mostly proprietary code that nobody but the original authors of the apps can touch.

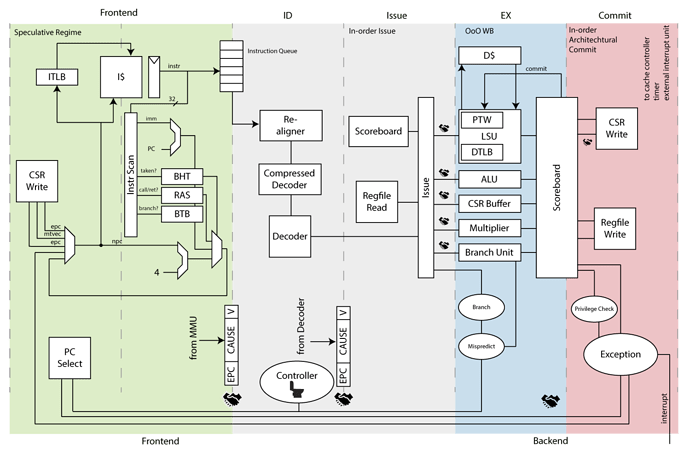

The OpenHW Group are starting with a planar 22nm FDSOI process node and getting speeds up to 1.7 GHz. They are using a very short 6-stage pipeline which should make it easy to get to higher clock rates as they move to smaller process nodes. On the other hand, they don’t have out-of-order execution and it looks like a simple architectural diagram, so it will take a lot more development to get performance that can match the ARM Cortex-A77 or x86.

Because NXP is implementing Ariane on the i.MX platform, that will make it much easier for Purism to switch to a future i.MX+RISC-V chip than starting with a whole new SoC from scratch, and it also means that there is a good chance that RYF devices can be made with a future i.MX+RISC-V SoC.

Despite the fact that i.MX 8M has caused all sorts of delays for the L5, it looks like Purism made the right choice in terms of the future by selecting the i.MX platform. It has future upgradeability (i.MX 8M Plus on Samsung 14nm FinFET) and it will likely have a free/open ISA in the future.

NXP is likely to implement this on a planar 28 or 22 nm node since it is so much cheaper to implement than a FinFET node, which means the i.MX 8M Plus at 14nm is likely to be more energy efficient and have better performance. The first iterations probably won’t include the neural processing unit, image signal processor or audio digital signal processor found in the i.MX 8M Plus, so the i.MX+RISC-V probably won’t be a good chip for phones or tablets, and it probably won’t have enough performance to use in a laptop.

In other words, the i.MX+RISC-V SoC probably won’t make that great of a device in terms of performance and energy efficiency. On the other hand, there is probably a market for people who want a usable RISC-V device, rather than an expensive dev board from SiFive that requires a bunch of proprietary software to run. SiFive is planning on using an Imagination PowerVR GPU with a proprietary driver, and its NPU will also likely require a proprietary driver as well.

The question is how many people on this forum would be willing to buy a i.MX+RISC-V device if Purism decides to make it?